Indice

POWER6

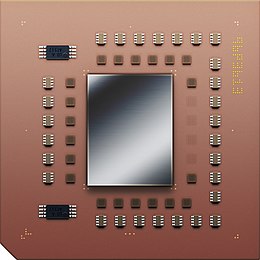

| POWER6 Central processing unit | |

|---|---|

| |

| Prodotto | 2007 |

| Progettato da | IBM |

| Predecessore | POWER5 |

| Successore | POWER7 |

| Specifiche tecniche | |

| Processo (l. canale MOSFET) | 65 nm |

| Set di istruzioni | Power |

| Microarchitettura | Power ISA v.2.05 |

| N° di core (CPU) | 2 |

| Cache L1 | 64+64 KB/core |

| Cache L2 | 4 MB/core |

| Cache L3 | 32 MB/chip (off-chip) |

Il POWER6 è un microprocessore a 64 bit progettato da IBM e successore del POWER5. Il processore è conosciuto anche come progetto eClipz. Uno dei maggiori obiettivi del progetto è portare i server non x86 su un'architettura comune. Il termine ipz è l'acronimo di iSeries, pSeries e zSeries.[1]

Il POWER6 venne annunciato alla IEEE International Solid-State Circuits Conference del febbraio 2006 e informazioni aggiuntive furono fornite durante il Microprocessor Forum nell'ottobre 2006.[2] La presentazione ufficiale del processore è avvenuta il 21 maggio 2007.[3] Mentre nell'ottobre del 2007 sono stati presentati da IBM i primi server basati sul processore.[4]

Descrizione

[modifica | modifica wikitesto]Il POWER6 utilizza 750 milioni di transistor e ha un die di 341 mm² con il processo a 65 nm.[5] Il processore ha una frequenza operativa di 3.5 GHz, 4.2 GHz, 4.7 GHz e 5 GHz. IBM ha affermato di essere arrivata con un esemplare da laboratorio a 6 GHz.[6] I primi esemplari sono stati prodotti nel 2005[7] ma i prodotti definitivi sono stati presentati nel 2007.[8]

Dr Frank Soltis, il progettista capo di IBM ha affermato che la società è riuscita a risolvere il problema delle correnti di leakage alle alte frequenze grazie all'utilizzo combinato della tecnologia a 65 e 90 nanometri durante lo sviluppo del processore.

Il processore è un progetto dual core e dispone di 128 KB di cache di primo livello (64 KB per le istruzioni e 64 KB per i dati) associativa a otto vie, con un progetto a due pipeline indipendenti per la lettura di due dati o la scrittura di uno solo nello stesso ciclo di clock[9]. Ogni core ha 4 MB di cache di secondo livello semicondivisa, ovvero ogni core ha una propria cache L2 ma tutti i core possono accedere alla cache degli altri tramite un bus veloce. I due core condividono una cache di terzo livello di 36 MB su un secondo chip, collegata al processore tramite un bus a 80 GB/s[5]. Internamente il processore ha un bus da 300 GB/s tra processori e cache interna.

Ogni core ha due unità aritmetiche per i numeri interi, due unità per i numeri in virgola mobile ed è in grado di gestire il SMT a due vie. L'unità in virgola mobile include buona parte della microarchitettura del processore come la pipeline 13-FO4[9] Il POWER6 inoltre gestisce la matematica in modalità decimale, gestisce cinquanta nuove istruzioni in virgola mobile per la matematica decimale e per la conversioni da binario a decimale[5]. La gestione dei numeri decimali è una caratteristica dei sistemi ZSeries e quindi il POWER6 doveva gestire questa aritmetica per poter aver successo nella missione iClipz[10].

Il POWER6 è dotato di un'unità AltiVec.

Il processore utilizza un sistema di correzione del duty-cycle del clock a 5 GHz, la rete di distribuzione del clock è in rame ed è composta da un canale a 3 µm ed uno a 1,2 µm. Il processore utilizza un'alimentazione duale a 0,8 e 1,2 Volt per definire lo zero logico e l'uno logico. L'alimentazione della SRAM è di circa 150 mV maggiore.[9]. La dissipazione termica è paragonabile a quella del POWER5.

Il POWER6 può essere collegato a 31 altri processori tramite due collegamenti da 50 GB/s e gestisce fino a 1024 partizioni virtuali.[5]

Prestazioni

[modifica | modifica wikitesto]Secondo IBM il processore ha raggiunto, nel test SPECfp2006, i 22.3 Gigaflops: esso quindi, secondo i dati IBM, risulta essere tre volte più potente del miglior processore Itanium disponibile al momento dei test. Anche nei test TCP-C, SPECjbb2005 e SPECint2006, il processore ha stabilito nuovi record.[11]

Note

[modifica | modifica wikitesto]- ^ A Mainframe Roadmap, su isham-research.co.uk (archiviato dall'url originale il 3 marzo 2016).

- ^ Microprocessor Forum nell'ottobre 2006, su in-stat.com. URL consultato il 17 ottobre 2006 (archiviato dall'url originale il 18 maggio 2007).

- ^ IBM annuncia il nuovo processore POWER6, su hwupgrade.it. URL consultato il 23 maggio 2007.

- ^ IBM tira fuori un blade Power6 e aggiorna AIX, su punto-informatico.it, 7-11-2007. URL consultato il 12 novembre 2007.

- ^ a b c d Fall Processor Forum: Power6 at 5 GHz, su heise.de (archiviato dall'url originale il 16 novembre 2007).

- ^ IBM's Power6 Processors to Hit 5.6GHz, su theregister.co.uk.

- ^ BM's Power6 Gets First Silicon as Power5+ Looms, su itjungle.com (archiviato dall'url originale il 25 novembre 2005).

- ^ IBM Cranks Up Its Server Chip, su pcworld.com. URL consultato il 3 maggio 2019 (archiviato dall'url originale il 30 aprile 2008).

- ^ a b c IBM Tips Power6 Processor Architecture, su informationweek.com. URL consultato il 17 ottobre 2006 (archiviato dall'url originale il 10 dicembre 2007).

- ^ An eCLipz Looms on the Horizon, su realworldtech.com.

- ^ CPU, IBM partorisce il Power6 dei record Punto Informatico

Voci correlate

[modifica | modifica wikitesto]Altri progetti

[modifica | modifica wikitesto] Wikimedia Commons contiene immagini o altri file su POWER6

Wikimedia Commons contiene immagini o altri file su POWER6

Collegamenti esterni

[modifica | modifica wikitesto]- (EN) Real World Tech, Dec 19, 2005, su realworldtech.com.

- (EN) InformationWeek, Feb 6, 2006, su informationweek.com. URL consultato il ottobre 17, 2006 (archiviato dall'url originale il 10 dicembre 2007).

- (EN) C, su news.com.com. URL consultato il 10 ottobre 2006 (archiviato dall'url originale il 3 gennaio 2013).

- (EN) Heise Online, Oct 12, 2006, su heise.de.